### FEATURES:

- Space saving SOD-882L package

- Ultra low capacitance

- Low leakage current

www.centralsemi.com

# DESCRIPTION:

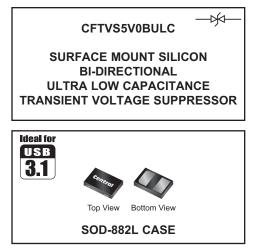

The CENTRAL SEMICONDUCTOR CFTVS5V0BULC is an ultra low capacitance, low leakage, fast response, bi-directional TVS in the space saving SOD-882L surface mount package. This device is designed to protect sensitive equipment connected to high speed data lines against ESD damage.

#### MARKING CODE: U

#### **APPLICATIONS:**

- High speed data line protection ideal for USB 3.1, Thunderbolt and HDMI 2.0 standards

- User interface protection

- Charging/power port protection

| MAXIMUM RATINGS: (T <sub>A</sub> =25°C)            | SYMBOL           |             | UNITS |

|----------------------------------------------------|------------------|-------------|-------|

| Peak Power Dissipation (8x20µs)                    | P <sub>PK</sub>  | 14          | W     |

| Electrical Fast Transient (IEC 61000-4-4) (5x50ns) | EFT              | 40          | А     |

| ESD Voltage (IEC 61000-4-2, Air)                   | V <sub>ESD</sub> | 20          | kV    |

| ESD Voltage (IEC 61000-4-2, Contact)               | V <sub>ESD</sub> | 20          | kV    |

| Operating Junction Temperature                     | ТЈ               | -55 to +125 | °C    |

| Storage Temperature                                | T <sub>stg</sub> | -55 to +150 | °C    |

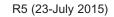

#### ELECTRICAL CHARACTERISTICS: (T<sub>A</sub>=25°C)

| Maximum<br>Reverse<br>Stand-off<br>Voltage | Reverse Breakdown <sup>-</sup><br>Stand-off Voltage Cu |                  | Test<br>Current | Maximum<br>Reverse<br>Leakage<br>Current | Clamping         |       | Typical<br>TLP Clamping<br>Voltage<br>(Note 1) |       | Typical<br>Dynamic<br>Resistance<br>(Note 1) | Typical<br>Junction<br>Capacitance<br>@ 0V Bias | Maximum<br>Junction<br>Capacitance<br>@ 0V Bias |

|--------------------------------------------|--------------------------------------------------------|------------------|-----------------|------------------------------------------|------------------|-------|------------------------------------------------|-------|----------------------------------------------|-------------------------------------------------|-------------------------------------------------|

| VRWM                                       | VBR                                                    | @ I <sub>T</sub> | ΙT              | I <sub>R</sub> @ V <sub>RWM</sub>        | V <sub>C</sub> @ | lpp 🛛 | V <sub>CL</sub> @                              | Ĵ IPP | R <sub>DYN</sub>                             | СJ                                              | СJ                                              |

| v                                          | MIN<br>V                                               | MAX<br>V         | mA              | nA                                       | v                | А     | v                                              | А     | Ω                                            | pF                                              | pF                                              |

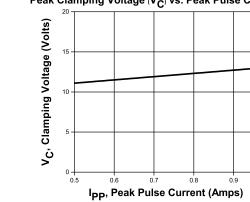

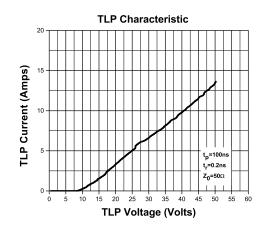

| 5.0                                        | <u> </u>                                               | 10               | 1.0             | 100                                      | 4.4              | 1.0   | 15                                             | 1.6   | 2.94                                         | 0.2                                             | 0.35                                            |

| 5.0                                        | 6.0                                                    | 10               | 1.0             | 100                                      | 14               | 1.0   | 20                                             | 3.3   |                                              |                                                 |                                                 |

Note 1: Transmission Line Pulse (TLP) conditions:  $Z_0=50\Omega$ , tp=100ns

R5 (23-July 2015)

SURFACE MOUNT SILICON **BI-DIRECTIONAL** ULTRA LOW CAPACITANCE TRANSIENT VOLTAGE SUPPRESSOR

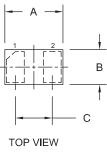

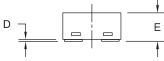

## SOD-882L CASE - MECHANICAL OUTLINE

| DIMENSIONS        |       |       |             |      |  |

|-------------------|-------|-------|-------------|------|--|

|                   | INC   | HES   | MILLIMETERS |      |  |

| SYMBOL            | MIN   | MAX   | MIN         | MAX  |  |

| А                 | 0.037 | 0.041 | 0.95        | 1.05 |  |

| В                 | 0.022 | 0.026 | 0.55        | 0.65 |  |

| С                 | 0.026 |       | 0.65        |      |  |

| D                 | 0.000 | 0.002 | 0.00        | 0.05 |  |

| Е                 | 0.012 | 0.016 | 0.30        | 0.40 |  |

| F                 | 0.018 | 0.022 | 0.45        | 0.55 |  |

| G                 | 0.008 | 0.012 | 0.20        | 0.30 |  |

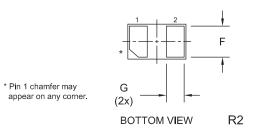

| SOD-882L (REV:R2) |       |       |             |      |  |

**PIN CONFIGURATION**

LEAD CODE: 1) Anode 1 2) Anode 2

MARKING CODE: U

SIDE VIEW

www.centralsemi.com

CFTVS5V0BULC

SURFACE MOUNT SILICON BI-DIRECTIONAL ULTRA LOW CAPACITANCE TRANSIENT VOLTAGE SUPPRESSOR

R5 (23-July 2015)

www.centralsemi.com

**Reverse Voltage** Leakage Current 8.40 1,000 V<sub>BR</sub>, Breakdown Voltage (Volts) I<sub>R</sub>, Reverse Current (nA) 8.38 100 8.36 8.34 10 8.32 I<sub>R</sub>= 1mA 8.30 <del>|</del> -25 1 + 25 50 75 100 125 50 ò T<sub>A</sub>, Ambient Temperature (°C) T<sub>A</sub>, Ambient Temperature (°C)

> T<sub>A</sub>=25°C f = 1.0 Mhz

Capacitance

V<sub>R</sub>, Reverse Voltage (Volts)

## **TYPICAL ELECTRICAL CHARACTERISTICS**

Peak Clamping Voltage (V<sub>C</sub>) vs. Peak Pulse Current (I<sub>PP</sub>)

75

0.5

0.4

0.3

0.2

0.1

0.0+0

C, Capacitance (pF)

1.0

R5 (23-July 2015)

V<sub>R</sub>=5V

125

100

CFTVS5V0BULC

SURFACE MOUNT SILICON BI-DIRECTIONAL ULTRA LOW CAPACITANCE TRANSIENT VOLTAGE SUPPRESSOR

**Power & Current Derating**

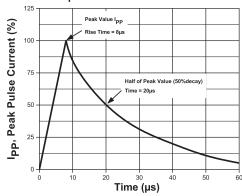

### 8x20µs Pulse Current Waveform

www.centralsemi.com

Ipp Current Derating in Percentage (%)

Р<sub>РК</sub>, PeakPower Derating or

125

100

75

50 ·

25

0+

25

50

75

T<sub>A</sub>, Ambient Temperature (°C)

100

125

150

R5 (23-July 2015)

# **OUTSTANDING SUPPORT AND SUPERIOR SERVICES**

#### **PRODUCT SUPPORT**

Central's operations team provides the highest level of support to insure product is delivered on-time.

- Supply management (Customer portals)

- Inventory bonding

- Consolidated shipping options

- Custom bar coding for shipments

- Custom product packing

#### DESIGNER SUPPORT/SERVICES

Central's applications engineering team is ready to discuss your design challenges. Just ask.

- Free quick ship samples (2<sup>nd</sup> day air)

- Online technical data and parametric search

- SPICE models

- Custom electrical curves

- Environmental regulation compliance

- Customer specific screening

- Up-screening capabilities

- Special wafer diffusions

- PbSn plating options

- Package details

- Application notes

- Application and design sample kits

- Custom product and package development

### CONTACT US

#### **Corporate Headquarters & Customer Support Team**

Central Semiconductor Corp. 145 Adams Avenue Hauppauge, NY 11788 USA Main Tel: (631) 435-1110 Main Fax: (631) 435-1824 Support Team Fax: (631) 435-3388 www.centralsemi.com

Worldwide Field Representatives: www.centralsemi.com/wwreps

Worldwide Distributors: www.centralsemi.com/wwdistributors

For the latest version of Central Semiconductor's **LIMITATIONS AND DAMAGES DISCLAIMER**, which is part of Central's Standard Terms and Conditions of sale, visit: <u>www.centralsemi.com/terms</u>

www.centralsemi.com